# Solidify the European FD-SOI ecosystem and accelerating its industrial deployment

**Martin LABRUNE**

Europe & French Public Affairs

**STMicroelectronics**

#### Agenda

1 STMicroelectronics overview

2 FD-SOI and applications

3 SOIL: roots, consortium, & objectives

4 SOIL project: WP structure, demonstrators, & impacts

#### Who we are

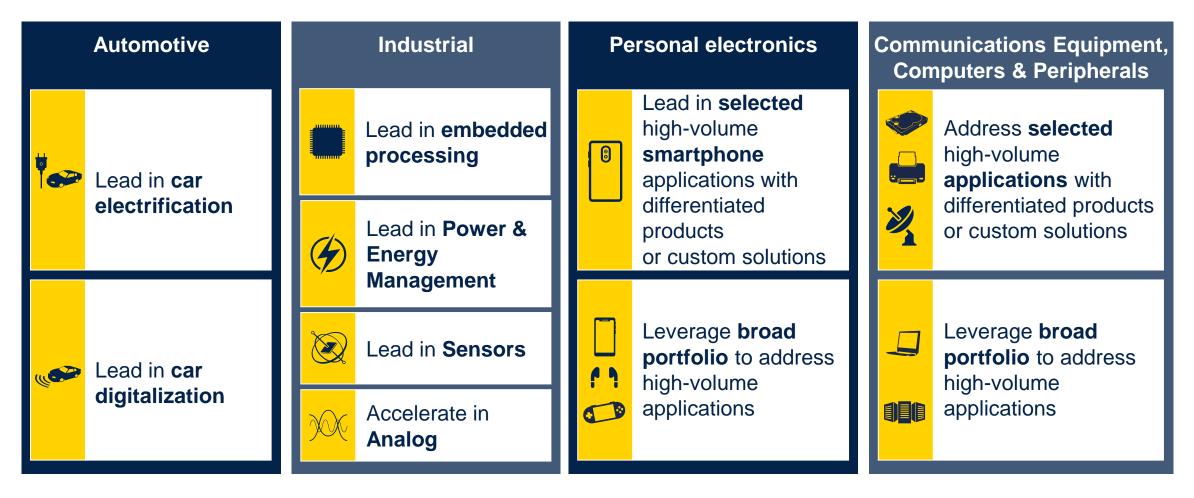

#### Four end markets

## Global presence & technology

Front-End (Wafer fabrication) Back-End (Assembly & Test)

China Shenzhen **Philippines** Calamba

**MEMS** for sensors & Micro-actuators

CMOS - power DMOS) FD-SOI CMOS Discrete, power MOSFET, IGBT

**Analog & RF CMOS**

FinFET through foundry

**Vertical intelligent power**

silicon carbide, gallium nitride

Smart power: BCD (bipolar -

**eNVM CMOS**

**Optical sensing solutions**

Packaging technologies Leadframe – Laminate – Sensor module – Wafer level **Sweden** Norrköping

France Crolles

Rousset Tours

Rennes

Italy Agrate Catania Marcianise

Morocco Bouskoura

Malta Kirkop

Malaysia Muar

Singapore

#### FD-SOI

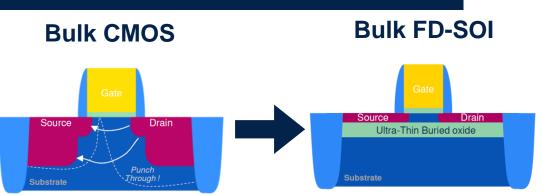

# FD-SOI was developed by STMicroelectronics, SOITEC, and CEA. It is a simpler process, compatible with bulk CMOS.

#### **UTBB FD-SOI features:**

- Better electrostatic characteristics

& thin channel controlled by the gate → lower leakage power

- Body biasing tuning performance/leakage trade-off, statically or dynamically

#### **Advantages:**

- Intrinsic RF & mm-W performance due to local isolation of devices vs substrate

- Possibility to bias transistor at a low voltage

- Wide operating voltage range for different applications

- → competitive performance, power, and area advantages

## FD-SOI market applications

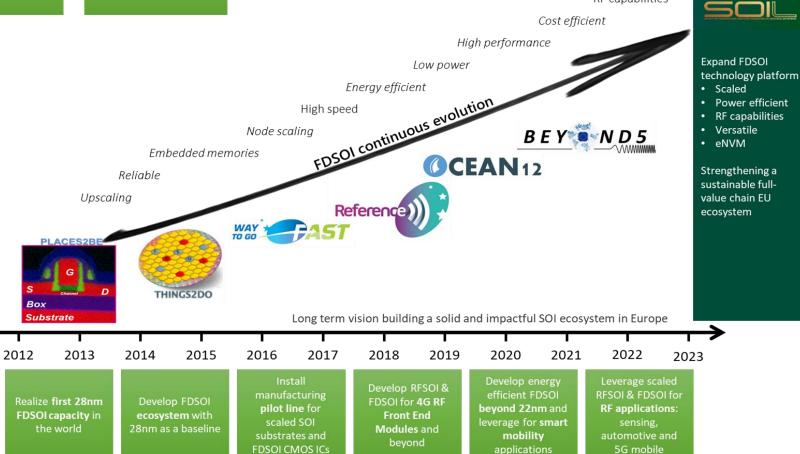

#### Embedded memory generations for MCUs leveraging the FDSOI technology evolution Integrate eNVM in BEOL WAKeMe<u>UP</u> Stor**≜**lge ePCM for Al Long term vision building a solid and impactful SOI ecosystem in Europe 2012 2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023 Establish an open ultra-low Setup an embedded Flash Setup an advanced MCU power technology and Develop & mature FDSOI technology pilot line for pilot line for smart mobility memory platform for IoT 28nm & ePCM for Edge AI innovative MCU based on ePCM on top of a applications, leveraging 28nm logic line prototyping

SOIL project : roots

RF capabilities

The SOIL project is rooted in 10+ years of successive European funded project aiming to develop a full FD-SOI ecosystem, from technology and desig platform providers, all the way to system and applications.

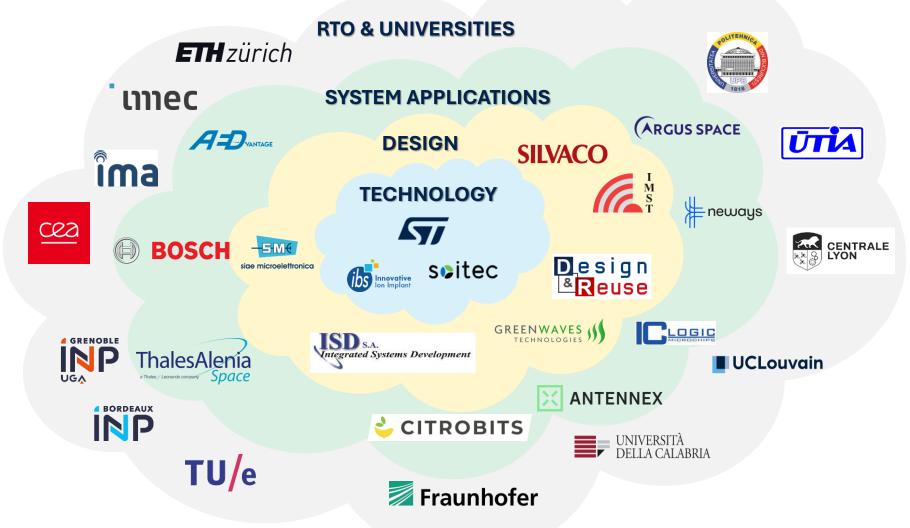

#### SOIL consortium: a European initiative

The SOIL project is funded by the CHIPS JU and the participant states.

It comprises 34 partners in 9 countries

36-month project with a 95.7 M€ budget

#### SOIL main objectives

1

European strategic sovereignty for semiconductor technology based on a resilient European value chain for FD-SOI technology

2

Achieve world-leading energy efficiency for sustainable semiconductor applications and production

3

Establish semiconductor, IP, and components for securing and leveraging European semiconductor leadership

R&D capacity building in key semiconductor technologies

#### ...all along the value chain

12

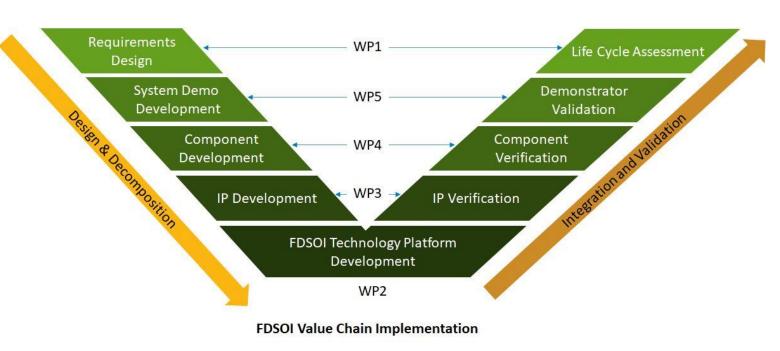

#### Work package: tasks along the value chain

# WP organization in the development chain System

Component

**Material**

FD-SOI Substrate enhancement

FD-SOI platform enablement & enhancement

Pathfinding development toward upcoming FD-SOI technology

Characterization

Model and simulation

Data converters

A=DVANTAGE

High-performance RF

Low power communication

Efficient computing

EDA for efficient and productive IP design

FD-SOI components for connectivity &

ARGUS SPACE

Edge Al

FD-SOI components for automotive

FD-SOI components for telecommunications and Space

Microphone array / sensor fusion

ASA-ML high speed wireline link

Automotive millimetre wave sensor

Active noise cancelling

Al-based inference

Rad-hard

Zero-energy communication

DESIGN

DLOGY

seitec

ROBI

Fraunhofer

#### SOIL demonstrators

#### Seven demonstrators, addressing three different markets

### Project impacts

#### Strengthen the ecosystem around European FD-SOI IC technology

ECSEL/KDT projects. Lab2Fab model.

FD-SOI ecosystem: enlarge existing environment, resulting from

Matching objectives of SRIA Foundation Technology Layers: Process Technology, Equipment, Materials And Manufacturing (eNVM, substrates) & Components, Modules and Systems Integration (sensing, sustainability)

Scientific: collaboration with RTOs, dissemination

**Economic/technological**: heart of digitalization (ADAS, IoT, etc) 18nm MCU

Environmental sustainability: quantitative evaluation of environmental targets for MCU production and networking equipment in Europe

# **Expected results in various areas**

### Acknowledgment

This project has received funding from the European Union's Horizon Europe research and innovation programme under the HORIZON-KDT-JU-2023-1-IA grant agreement No 101139785.

The following states have also contributed to the funding of that project: Belgium, Czechia, France, Italy, Netherlands, Romania, and Switzerland.

The views and opinions expressed are however those of the author(s) only and do not necessarily reflect those of the European Union or CHIPS. Neither the European Union nor the granting authority can be held responsible for them.

# Our technology starts with You

© STMicroelectronics - All rights reserved.

ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>.

All other product or service names are the property of their respective owners.